## **IGCSE** Computer Science

| N | am | e | : |  |

|---|----|---|---|--|

|   |    |   |   |  |

Chapter 10 Test: Boolean Logic

Q1

Consider this logic expression.

(a) Draw a logic circuit for this logic expression.

Each logic gate must have a maximum of two inputs.

Do not simplify this logic expression.

(b) Complete the truth table from the given logic expression.

| A | В | С | ALE | Working space | х     |

|---|---|---|-----|---------------|-------|

| 0 | 0 | 0 | 0   | 0             | 0     |

| 0 | 0 | 1 | 0   | 0             | 0     |

| 0 | 1 | 0 | 0   | 1             | 1     |

| 0 | 1 | 1 | 0   | 0             | 01    |

| 1 | 0 | 0 | 0   | 0             | 0     |

| 1 | 0 | 1 | 0   | 0             | 0     |

| 1 | 1 | 0 | 1   |               | ì     |

| 1 | 1 | 1 | -[  | 0             | 1 100 |

- 7 NAND, OR and XOR are three types of logic gate.

- (a) Four statements are shown about the logic gates.

Tick ( $\checkmark$ ) to show which statements apply to each logic gate. Some statements may apply to more than one logic gate.

| Statement                                                         | NAND<br>(✓) | OR<br>(✓) | XOR<br>(✓) |

|-------------------------------------------------------------------|-------------|-----------|------------|

| if both inputs are 1, the output is 1                             |             | /         | /          |

| if both inputs are different from each other, the output is 1     | /           |           | V          |

| if both inputs are 0, the output is 0                             | Ka          | V         | V /        |

| if both inputs are the same as each other, the output is always 0 |             |           | 1/         |

| (b) | NAND, OR | , XOR, NOR an | d NOT are | all examples | of logic gates. |

|-----|----------|---------------|-----------|--------------|-----------------|

|-----|----------|---------------|-----------|--------------|-----------------|

| State the name of one other logic gate and comple | te its truth table |  |

|---------------------------------------------------|--------------------|--|

|---------------------------------------------------|--------------------|--|

| Logic gateAND | / |

|---------------|---|

|---------------|---|

Truth table:

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0 .    |

| 1 | 1 | 19 10  |

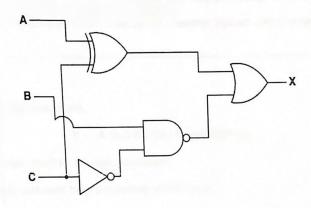

Consider the logic circuit:

(a) Write a logic statement to match the given logic circuit.

(A XOR OR (E NAMD (NOTC))

[3]

(b) Complete the truth table for the given logic circuit.

|   | - | c | Working space        |                | X |

|---|---|---|----------------------|----------------|---|

| A | В |   | A YOR C              | MAR BNAMD NOTC |   |

| 0 | 0 | 0 | 0                    |                | 1 |

| 0 | 0 | 1 | 1                    | 1              | 1 |

| 0 | 1 | 0 | 0                    | 0              | 0 |

| 0 | 1 | 1 |                      | 1              | 1 |

| 1 | 0 | 0 | 10 - 10 p. 10 - 10 M |                |   |

| 1 | 0 | 1 | 0                    | 1              | 1 |

| 1 | 1 | 0 |                      | 0              | 1 |

| 1 | 1 | 1 | 0                    |                |   |

[4]

8 Consider the following logic statement:

## X = (((A AND NOT B) OR (NOT (B NOR C))) AND C)

(a) Draw a logic circuit to represent the given logic statement.

Do **not** attempt to simplify the logic statement. All logic gates must have a maximum of **two** inputs.

(b) Complete the truth table for the given logic statement.

| Α | В | С | AMD E' | Morking spa | or. | х  |

|---|---|---|--------|-------------|-----|----|

| 0 | 0 | 0 | ð      | 0           | 0   | 0  |

| 0 | 0 | 1 | 6      |             |     | 1  |

| 0 | 1 | 0 | 0      |             |     | 0  |

| 0 | 1 | 1 | 0      |             | 1   |    |

| 1 | 0 | 0 |        | 0           |     | 0  |

| 1 | 0 | 1 | 1      | T.          |     | 1  |

| 1 | 1 | 0 | 0      |             |     | 0  |

| 1 | 1 | 1 | 6      |             | 1   | CV |